Cosimulação MATLAB (Simulink) + Modelsim/QuestaSim

Aspeto

Tutorial de como realizar co-simulação de módulos de Hardware (HDL) junto com o Simulink (MATLAB).

A seguir, o comando do Matlab para chamar o tutorial do toolbok HDL Verifier.

helpview(fullfile(docroot,'toolbox','hdlverifier','helptargets.map'),'EDACosimAssistTutorialSL')

- Ter o código fonte dos módulos em VHDL

- Abrir o MATLAB e utilizar o comando cosimWizard (Toolbox HDL Verifier)

cosimWizard

- Na primeira interface, selecionar as opções, Simulink e Modelsim e definir o caminho da ferramenta QuestaSim ou ModelSim

- Na próxima tela (após apertar em NEXT), insira todos os arquivos VHDL dos módulos em hardware.

- Após clicar novamente em NEXT, será gerado um script de compilação dos módulos em VHDL (utilizando o ModelSim/QuestaSim) que irá verificar a consistência dos arquivos.

Em seguida, na próxima tela, escolha (1) a entidade que representa o TOP LEVEL do módulo em Hardware e em seguida apague o parâmetro -novopt (2). Manter a comunicação com Sockets.

- Em seguida, defina cada porta de entrada e saída do módulo top, se é clock, reset, entrada ou saída.

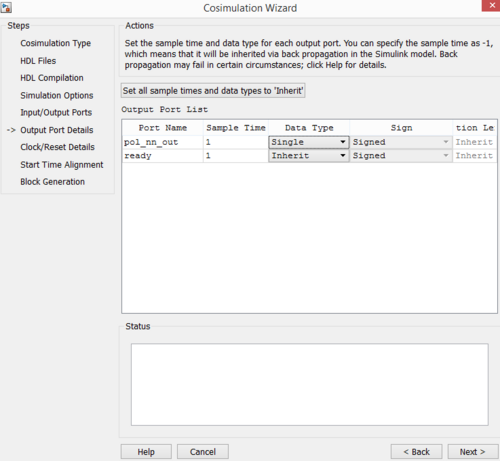

- Finalmente, selecione o formato de dados das saídas (Inherit para herdar o tipo automaticamente, single e double para floating point, ou FixedPoint)

- Na próxima tela, são definidos os tempos de clock e reset.